- 您现在的位置:买卖IC网 > Sheet目录2001 > ISL12058IUZ (Intersil)IC RTC/CALENDAR I2C-BUS 8-MSOP

6

FN6756.0

June 15, 2009

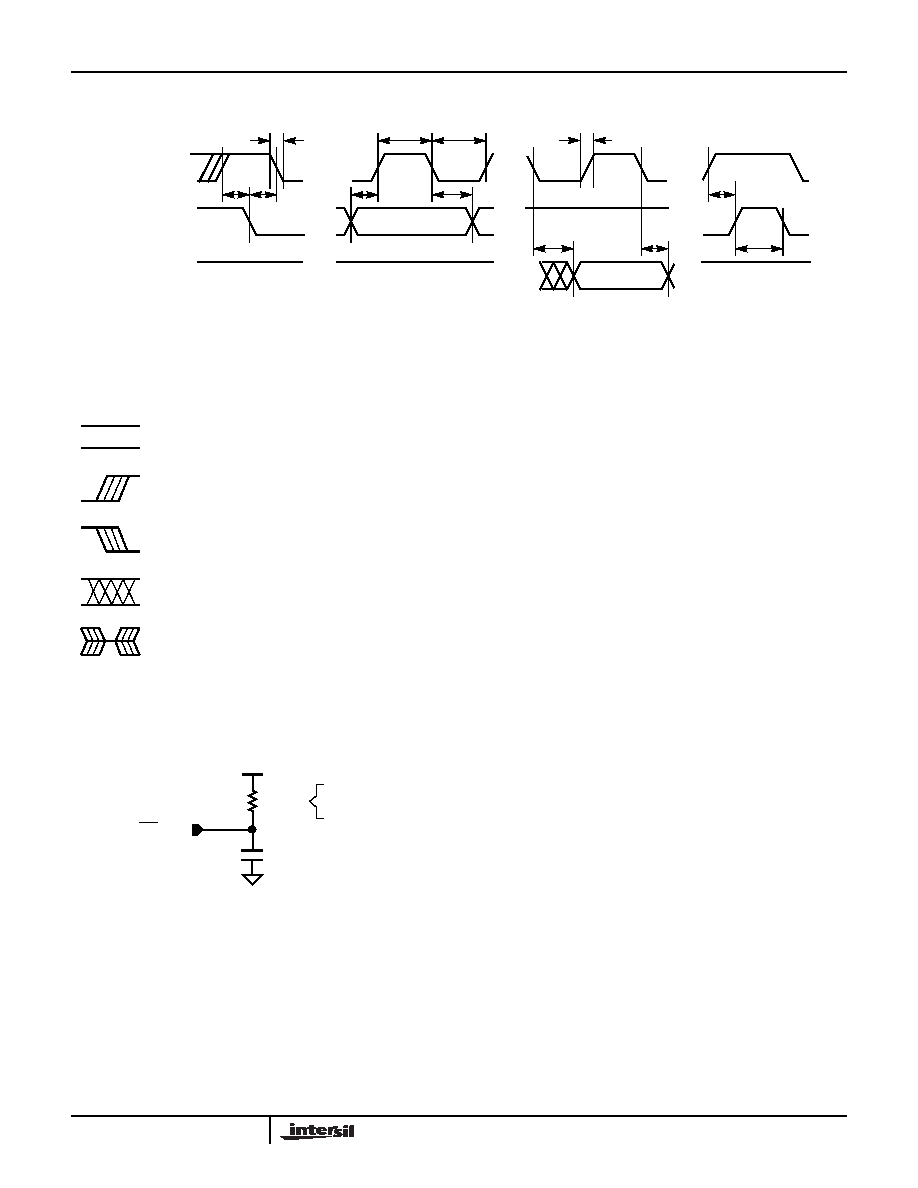

SDA vs SCL Timing

Symbol Table

tSU:STO

tDH

tHIGH

tSU:STA

tHD:STA

tHD:DAT

tSU:DAT

SCL

SDA

(INPUT TIMING)

SDA

(OUTPUT TIMING)

tF

tLOW

tBUF

tAA

tR

WAVEFORM

INPUTS

OUTPUTS

Must be steady

Will be steady

May change

from LOW

to HIGH

Will change

from LOW

to HIGH

May change

from HIGH

to LOW

Will change

from HIGH

to LOW

Don’t Care:

Changes Allowed

Changing:

State Not Known

N/A

Center Line is

High Impedance

FIGURE 1. STANDARD OUTPUT LOAD FOR TESTING THE

DEVICE WITH VDD = 3.0V, VPULLUP = 5.0V

SDA,

IRQ/FOUT

1533

Ω

100pF

5.0V

FOR VOL= 0.4V

AND IOL = 3mA

EQUIVALENT AC OUTPUT LOAD CIRCUIT FOR VDD = 3.0V

ISL12058

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL12059IBZ

IC RTC/CALENDAR I2C-BUS 8-SOIC

ISL12082IUZ

IC RTC I2C LO-POWER 10-MSOP

ISL1208IU8-TK

IC RTC/CALENDAR I2C 8-MSOP

ISL1209IU10-TK

IC RTC/CALENDAR I2C 10-MSOP

ISL1218IUZ

IC RTC LP BATT BACKED SRAM 8MSOP

ISL1219IUZ-T

IC RTC LP BATT BACK SRAM 10MSOP

ISL1220IUZ

IC RTC LP BATT BACK SRAM 10MSOP

ISL1221IUZ

IC RTC LP BATT BACK SRAM 10MSOP

相关代理商/技术参数

ISL12058IUZ-T

功能描述:实时时钟 REAL TIME CLK W/ ALARM & TIMR FUNCTNS RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12059

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Cost and Low Power I2C Bus? Real Time Clock/Calendar

ISL12059IBZ

功能描述:实时时钟 REAL TIME CLK W/ ALARM & TIMR FUNCTNS RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12059IBZ-T

功能描述:实时时钟 REAL TIME CLK W/ ALARM & TIMR FUNCTNS RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL1208

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Power RTC with Battery Backed

SRAM

ISL1208_06

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Power RTC with Battery Backed SRAM

ISL12082

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:I2C-Bus? Real Time Clock with Two Interrupts, Alarm, and Timer

ISL12082IB8Z

功能描述:实时时钟 LW PWR RTC W/ALARM & TIMR FUNCTIONS 8LD RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube